半導体の先端パッケージ技術は、次世代デバイスの開発において極めて重要な役割を果たしています。技術の進化に伴い、従来のパッケージ手法ではサイズ、性能、消費電力の面で限界が生じています。先端パッケージは、これらの課題を解決し、機能性の向上、小型化による性能改善、低消費電力、高信頼性を実現します。

最近の技術革新の中でも、特にファンアウトパッケージはその汎用性とスケーラビリティの高さから急速に注目を集めています。ファンアウトパッケージは、プロセッサー、センサー、高帯域メモリ(HBM)など複数の半導体デバイスを1つの高性能パッケージに統合することが可能です。設計や形状の柔軟性も高く、機能性を維持しつつコストを抑えた小型モジュールの実現が可能です。

本ブログでは、MESがファンアウトパッケージ工程を最適化する2つの主要なユースケースを紹介します。

ユースケース①:チップ(ダイ)のトラッキング

課題

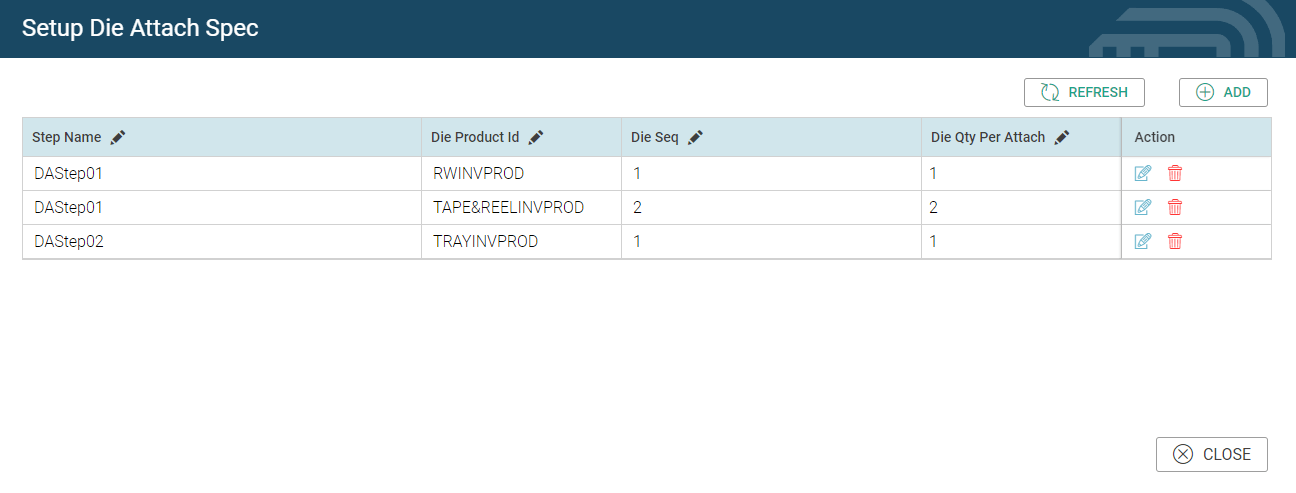

ファンアウトパッケージング工程では、複数のチップ(ダイ)を基板に取り付ける際に、どのチップ(ダイ)がどの位置に、どの順序で取り付けられるかをモデル化することが重要です(下図の図1参照)。

ひとつの基板上の位置に、異なる種類のチップ(ダイ)が取り付けられる可能性があるため、正確なチップ(ダイ)取り付け順序の設定は非常に重要です。

メリット

SmartFactory MES for ATPは、チップ(ダイ)が基板にどのように取り付けられるかをモデリングおよびトラッキングする機能を提供し、実行時のミス防止によって運用効率の向上を実現します。

さらに、事前定b義されたオートメーション化シナリオにより、各種製造装置との自動連携にかかる工数を最小限に抑えることができます。

メリット

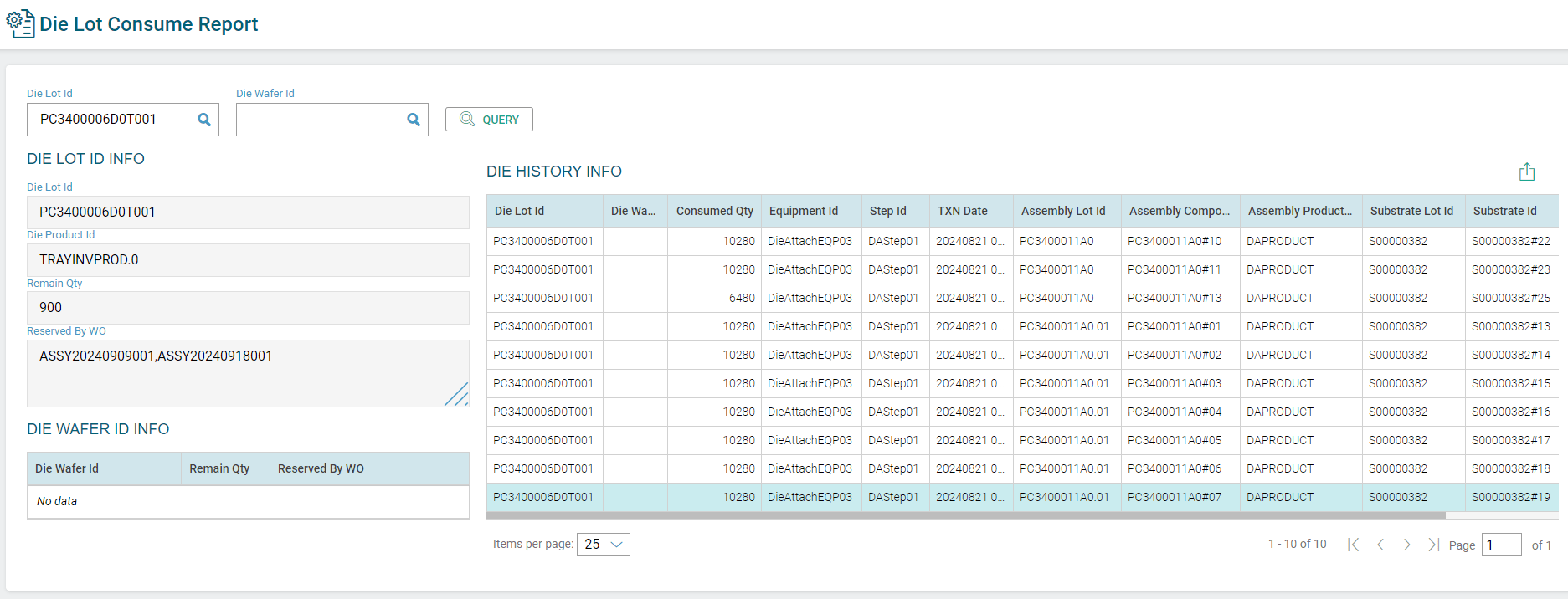

SmartFactory MES for ATPは、消費されたチップ(ダイ)の数量およびチップ(ダイ)/基板の位置情報に関する包括的なトレーサビリティレポートを提供します。

本ソリューションは、製品の種類を問わず(AIプロセッサからHBMモジュールまで)、製造中に発生する問題の影響を最小限に抑え、根本原因の特定するための時間を短縮するのに必要な正確かつ詳細な情報を提供します。

まとめ

The SmartFactory MES for ATP:

- 基板上のチップ(ダイ)の取り付け位置と順序をモデリングすることが可能で、これにより、ファンアウト工程全体にわたって、チップ(ダイ)・基板・ロットの包括的かつ正確なトレーサビリティが実現されます。

- 消費された材料、製造用治具の使用履歴、工程の系譜、および装置の稼働状況と保守履歴等に関する包括的なトレーサビリティ機能を提供します。

これにより、製造オペレーションの可視性と監査適合性が担保されます。 - ロットの移動を追跡し、生産の進捗を監視し、MESとオートメーション化された装置との間で正確なデータ同期を維持することで、ファンアウト工程全体の管理を実現します。

次のステップ

半導体の先端パッケージ技術は革新的かつ急速に進化しています。

SmartFactory MES for ATPがどのように多様なユースケースに対応しているかをぜひご覧ください。次回のブログでは、先端パッケージ工場における完全自動化の実現についてご紹介します。

SmartFactory MES for ATPの詳細についてはこちらからお問い合わせください。