In semiconductor manufacturing, the industry often draws a clean conceptual line between “upstream” and “downstream.” The rationale is that upstream steps prepare the material, while downstream is where real manufacturing happens. Crystal growth and wafering happen upstream. Wafer fabrication, test, and assembly happen downstream. In today’s semiconductor manufacturing environment, these boundaries are no longer so clean-cut.

As device complexity increases and tolerance for variation shrinks, what happens during wafer substrate manufacturing is no longer a prelude to manufacturing. It is manufacturing. The level of execution discipline applied there increasingly determines what the fab can—and cannot—achieve. It also requires manufacturers to rethink how execution is managed at the very front of the semiconductor lifecycle.

Wafer quality starts upstream

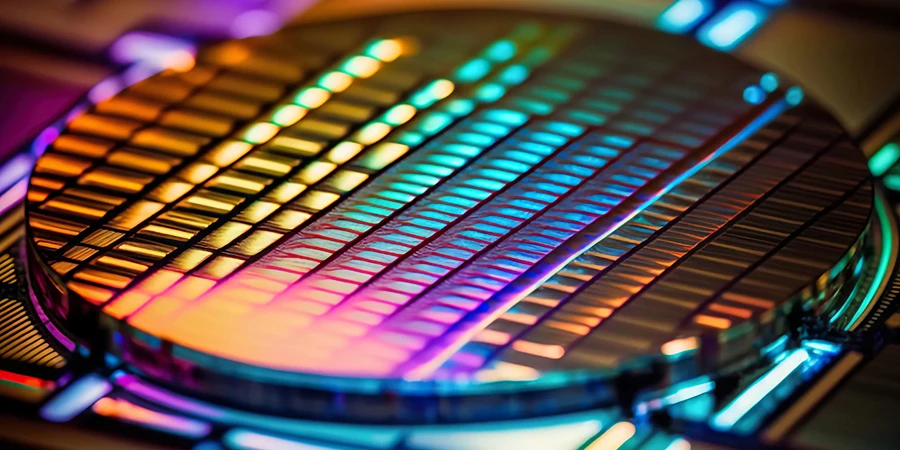

Every semiconductor device begins with a wafer whose physical properties are established long before it enters a fab. Characteristics such as crystal orientation, defect density, thickness uniformity, and surface quality are set during crystal growth and wafering. Once established, these attributes propagate forward through every downstream process step. When variation is introduced at this stage, the fab can detect and compensate for some effects—but it cannot undo them.

While this reality is not new, scaling has made it a much bigger problem.

Larger wafers, tighter geometries, and advanced device architectures amplify the impact of early‑stage variation. Small inconsistencies that once fell within acceptable margins now create meaningful downstream consequences. In that environment, treating substrate manufacturing as a loosely controlled preparatory phase is a growing liability.

How scaling changed the rules

Historically, many wafer substrate operations evolved in environments that prioritized material science and process development over high‑volume execution. That made sense when volumes were lower and variability could be managed through expertise and manual intervention, but times have changed. Substrate manufacturers are scaling production to support growing demand across logic, memory, power, and specialty devices.

Scaling does not simply increase output—it multiplies the consequences of inconsistency. Practices that were successful in pilot lines or lower‑volume environments become fragile when throughput increases, shift structures expand, and product mixes grow more complex. At scale, consistency cannot rely on individual expertise alone. It requires systems that enforce standard execution, manage change deliberately, and make process behavior visible in real time.

This naturally pushes manufacturers toward more formal execution control. However, applying “standard” downstream playbooks upstream often exposes a mismatch between the tools and the reality of substrate workflows.

Shortcomings of execution models designed for downstream

Manufacturing Execution Systems (MES) bring order and control to complex operations, so many manufacturers turn to the MES to bring order to substrate manufacturing before impacts are felt downstream. That instinct is correct—but not all MES platforms are created with substrate manufacturing in mind. This is where traditional execution models—and many MES implementations—begin to show strain.

Wafer substrate operations differ fundamentally from downstream fab and packaging environments. Process steps are longer; material transformations are physical and irreversible. Genealogy—from seed crystal, to ingot, to wafer—is central to understanding quality. Additionally, workflows do not resemble the short, tool‑centric cycles common in fabs.

When execution systems designed for other environments are forced upstream, manufacturers often compensate with workarounds: custom logic, external spreadsheets, manual handoffs. Over time, these adaptations create fragility instead of control, and the upstream processes most responsible for downstream outcomes remain under‑modeled and inconsistently enforced.

Existing approaches to traceability often exacerbate this gap, as they are downstream-focused— helping to identify outcomes rather than prevent issues at their source.

Moving traceability from discovery to origin

Traceability is often discussed in the context of yield analysis and failure investigation. While this is important, traceability delivers the greatest value when it exists where problems originate, not where they are discovered.

When substrate‑level genealogy and process history are incomplete or loosely structured, downstream teams are left to infer root causes rather than identify them. Investigations take longer. Corrective actions are broader than necessary. Confidence in decisions erodes.

Instead, traceability needs to be built into upstream execution, with each wafer carrying a clear, system‑enforced record of how it was produced. This enables manufacturers to prevent problems from propagating, rather than search for the root cause after the fact.

In an industry where downstream rework and scrap are exceptionally costly, that distinction matters. The road to achieving that requires a broader shift, toward an execution standard that is reliable by design and can sustain repeatable performance at true manufacturing scale.

What is “production grade” execution?

As substrate manufacturing moves into the critical path of semiconductor production, expectations change. The question is no longer whether a process can be made to work, but whether it can be run reliably, repeatedly, and at scale.

Production‑grade execution means more than automation. It means:

- Standardized workflows that reflect real manufacturing practices.

- Controlled change that preserves stability while enabling improvement.

- Real‑time visibility into execution, not just historical reporting.

- Reliability measured in uptime and consistency, not flexibility alone.

Manufacturers already hold these expectations for mission‑critical fabs, but they are increasingly recognizing the same need to be employed upstream.

Bringing fab‑level discipline forward

Semiconductor manufacturing has always been an exercise in managing complexity. What is changing is where that complexity must be controlled.

As devices grow more advanced and margins for error shrink, the industry can no longer afford a disconnect between upstream material preparation and downstream device fabrication. Execution discipline must span the full lifecycle—from crystal growth through finished product.

Manufacturers that treat wafer substrate operations as critical infrastructure, rather than a handoff, position themselves to scale with confidence. They reduce downstream risk, shorten learning cycles, and create a stronger foundation for continuous improvement.

In the end, the lesson is straightforward: by the time a wafer reaches the fab, much of the outcome is already set in motion. The manufacturers who recognize that—and act on it—will be better equipped for the next era of semiconductor production.